【Vivado那些事儿】-VIO原理及应用 - CSDN博客

2021年9月6日 · VIO(Virtual Input/Output)是Vivado设计工具中的一种IP核,用于对FPGA器件中的信号进行读写操作。VIO IP核可以直接与FPGA器件中的任意信号相连,并通过JTAG接口对这些信号进行读写操作。

VIO引脚在CAN通信中的重要性与电平匹配 - CSDN博客

2023年8月4日 · 独立供电是指usb芯片和串口负载使用不同的电源,对于包含vio电源引脚的芯片,需要单独考虑vio引脚电路接法,当vio和串口负载使用同一电压源不会存在问题,当vdd5、vio和串口负载未使用同一电压源时,此时需注意上电时序。当txd侧器件无电,nmos不导通,rxd和 ...

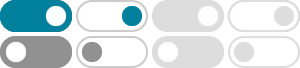

在双电源运行中,数字电路电源 vio 为逻辑信号引脚 (l1 – l4) 和控制信号引脚(slr、 DIR、M0、M1、TERM_TX、TERM_RX 和 /SHDN)供电。 此电源可在 1.65V 至 5.5V 的电压范围内运行,从而

bat、cvdd、dvdd 和 vio 引脚是 bq79600-q1 中的电源,用于为芯片中的不同模块供电。 BAT 引脚是为内部 LDO 和唤醒电路供电的电池电源输入。 使用反向唤醒功能时,应通过一个 10Ω 电阻将该引脚

TCAN1145-Q1: VIO 端口掉电一段时间后进入什么状态 - 接口论坛

2023年3月2日 · 电路方案是1145 vio端口供电为3.3v,与mcu供电为统一电源。 由于MCU可能会涉及到断电复位重启,即3.3V电源会掉电一段时间。 那么此时,CAN收发器在3.3V断电时会处于什么状态?

深入了解基于CANoe的VIO系统应用 - 北汇信息 - 博客园

2024年8月21日 · VIO System的板卡已经安装完成后,为VIO8904电源板卡进行供电,如下图,VIO系统内部板卡之间以3Gbps的HSBL连接通信,并通过RJ45千兆Ethernet网线将上行链路通信板卡VIO6020的ETH1网口连接至CANoe所在的上位机PC,同时可以使用另外2个RJ45 Ethernet端口级联更多VIO System或含 ...

VIO你用对了吗 - CSDN博客

2020年11月6日 · Vivado中的VIO(Virtual Input/Output) IP核是一种用于调试和测试FPGA设计的IP核。它允许设计者通过使用JTAG接口读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO IP核

CH343G VIO相关问题 - 沁恒微电子社区

2023年12月7日 · 1、若vio未上电时,芯片处于复位态,此时usb不会识别; 2、VIO断电后,芯片也会进入复位态,此时USB也会消失; 若您那边有其他需求,可邮件至我司技术邮箱tech@wch.cn进行沟通。

深入了解基于CANoe的VIO系统应用-电子工程世界

2024年9月3日 · VIO System的板卡已经安装完成后,为VIO8904电源板卡进行供电,如下图,VIO系统内部板卡之间以3Gbps的HSBL连接通信,并通过RJ45千兆Ethernet网线将上行链路通信板卡VIO6020的ETH1网口连接至CANoe所在的上位机PC,同时可以使用另外2个RJ45 Ethernet端口级联更多VIO System或含 ...

SM系列全隔离CAN收发芯片的“家族成员”,你了解多少?

2023年8月16日 · 不同于ctm系列收发器,4款sm系列芯片具有独立的vio逻辑供电引脚,用户只需要保证vio电压与 mcu 接口电压一致,芯片就能正常工作。 产品典型应用电路如图 3所示,同一收发器可兼容不同供电MCU。